In this video from the HPC User Forum at Argonne, Steve Scott from Cray presents: The Cray Shasta Architecture. The DOE has selected the Shasta architecture to power all three of their planned Exascale systems coming to Argonne, ORNL, and LLNL.

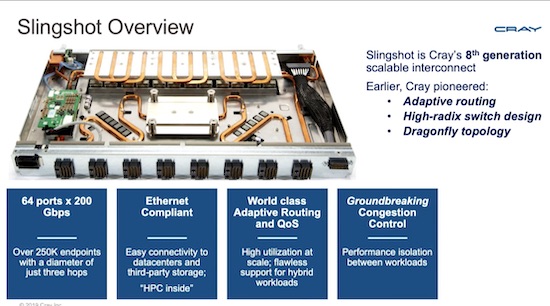

Increasingly, high-performance computing systems today need to be able to handle massive converged modeling, simulation, AI and analytics workloads. With these needs driving scientific discovery and technology, the next generation of supercomputing will be characterized by the fastest exascale performance, data-centric workloads and diversification of processor architectures. Shasta is an entirely new design, created from the ground up to address these needs. Built to be data-centric, it runs the fastest and most diverse workloads all at the same time. Hardware and software innovations tackle system bottlenecks in processing, data movement and I/O. It eliminates the distinction between clusters and supercomputers, providing a rich software and system interconnect in different form factors. It allows for multiple processor and accelerator architectures and a choice of system interconnect technologies, including our new Cray-designed and developed interconnect we call Slingshot.”

Steve Scott serves as Senior Vice President and Chief Technology Officer, responsible for guiding the long-term technical direction of Cray’s supercomputing, storage and analytics products. Dr. Scott rejoined Cray in 2014 after serving as principal engineer in the Platforms group at Google and before that as the senior vice president and chief technology officer for NVIDIA’s Tesla business unit. Dr. Scott first joined Cray in 1992, after earning his Ph.D. in computer architecture and BSEE in computer engineering from the University of Wisconsin-Madison. He was the chief architect of several Cray supercomputers and interconnects. Dr. Scott is a noted expert in high performance computer architecture and interconnection networks. He holds 41 U.S. patents in the areas of interconnection networks, cache coherence, synchronization mechanisms and scalable parallel architectures. He received the 2005 ACM Maurice Wilkes Award and the 2005 IEEE Seymour Cray Computer Engineering Award, and is a Fellow of IEEE and ACM. Dr. Scott was named to HPCwire’s “People to Watch in High Performance Computing” in 2012 and 2005.